Pipelined ADC Design

Course: ENG 581 - Pipelined ADC Design

Authors: Sayankar, Rutvik and Patel, Dev

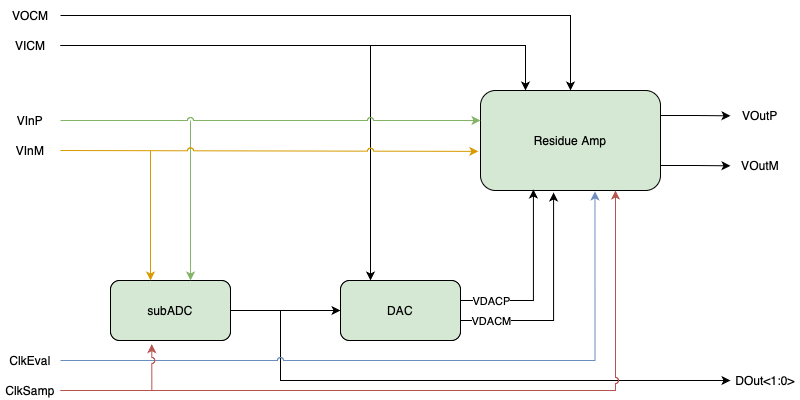

The project aimed to design the first stage of a 12-bit pipelined ADC focusing on the residue amplifier, sub-ADC, and MDAC to meet high-performance specifications with minimal power consumption.

Design Highlights

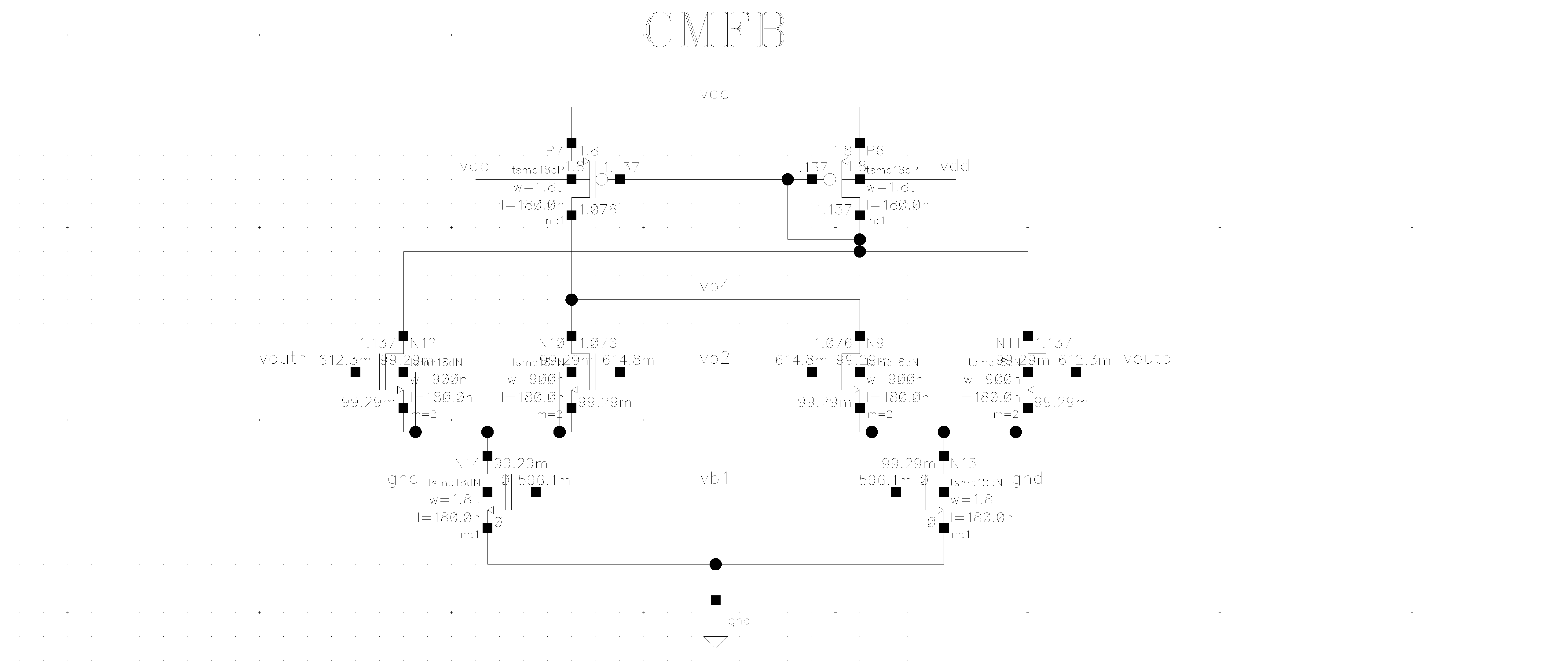

- Residue Amplifier: Folded-cascode opamp for high bandwidth and low power.

- Sub-ADC: Utilized pre-amplifier-based comparators for improved noise immunity and speed.

- MDAC: Transmission gate-based MUX for efficient signal switching.

.png)

.png)

.png)

.png)

Simulation Results

Key parameters such as SNDR, SFDR, and power consumption were evaluated. The design demonstrated effective performance, meeting the required specifications for high-speed analog-to-digital conversion.